MMU란?

메모리 관리 유닛(MMU, Memory Management Unit)은 CPU의 구성 요소로, 가상 주소를 물리 주소로 변환하고 메모리 보호를 제공하는 역할을 한다.

주소 변환이란?

주소 변환(Address Translation)은 가상 주소를 물리 주소로 변환하는 과정이다. 이 과정은 주로 페이지 테이블을 참조하여 수행된다.

TLB의 등장 배경

페이지 테이블은 가상 메모리 시스템에서 주소 변환을 가능하게 하지만, 매번 페이지 테이블을 참조하는 것은 시간과 자원을 소모한다. 특히, 프로세스가 많은 페이지를 사용하는 경우, 페이지 테이블 조회는 큰 성능 저하를 초래할 수 있다. TLB는 이러한 문제를 해결하기 위해 도입되었으며, 페이지 테이블의 일부를 고속 캐시에 저장하여 자주 접근하는 페이지를 빠르게 조회할 수 있게 한다.

TLB (Translation Lookaside Buffer)란

- 자주 참조되는 가상 메모리 주소를 실제 메모리 주소로 매핑시 성능 개선을 위해 MMU에서 사용하는 고속 캐시

- 논리 메모리 주소를 물리적인 주소로 변환할 때 캐싱된 페이지 번호를 병렬 검색을 통해 빠르게 물리 주소로 변환

- 가장 최근에 참조된 페이지를 TLB에 저장하여 병렬판독회로(HW)로 페이지에 바로 접근

특징

1. 변환 결과 테이블 : 페이지 테이블 통하지 않고 TLB 내 물리 주소 변환 결과를 통해 물리주소 접근

2. 특수 고속 캐시 : 페이지 테이블 항목에 대한 특수 고속 캐시를 사용해 메모리 참조시간 단축

TLB의 주요 기능:

1. 주소 변환 속도 향상: 페이지 테이블을 직접 참조하는 것보다 TLB를 사용하면 주소 변환 속도가 훨씬 빨라진다.

2. 캐시 효과: 자주 접근하는 페이지 테이블 항목을 캐시에 저장하여 페이지 테이블 조회 시간을 절약한다.

3. 메모리 액세스 최적화: CPU가 메모리에 빠르게 접근할 수 있게 하여 전체 시스템 성능을 향상시킨다.

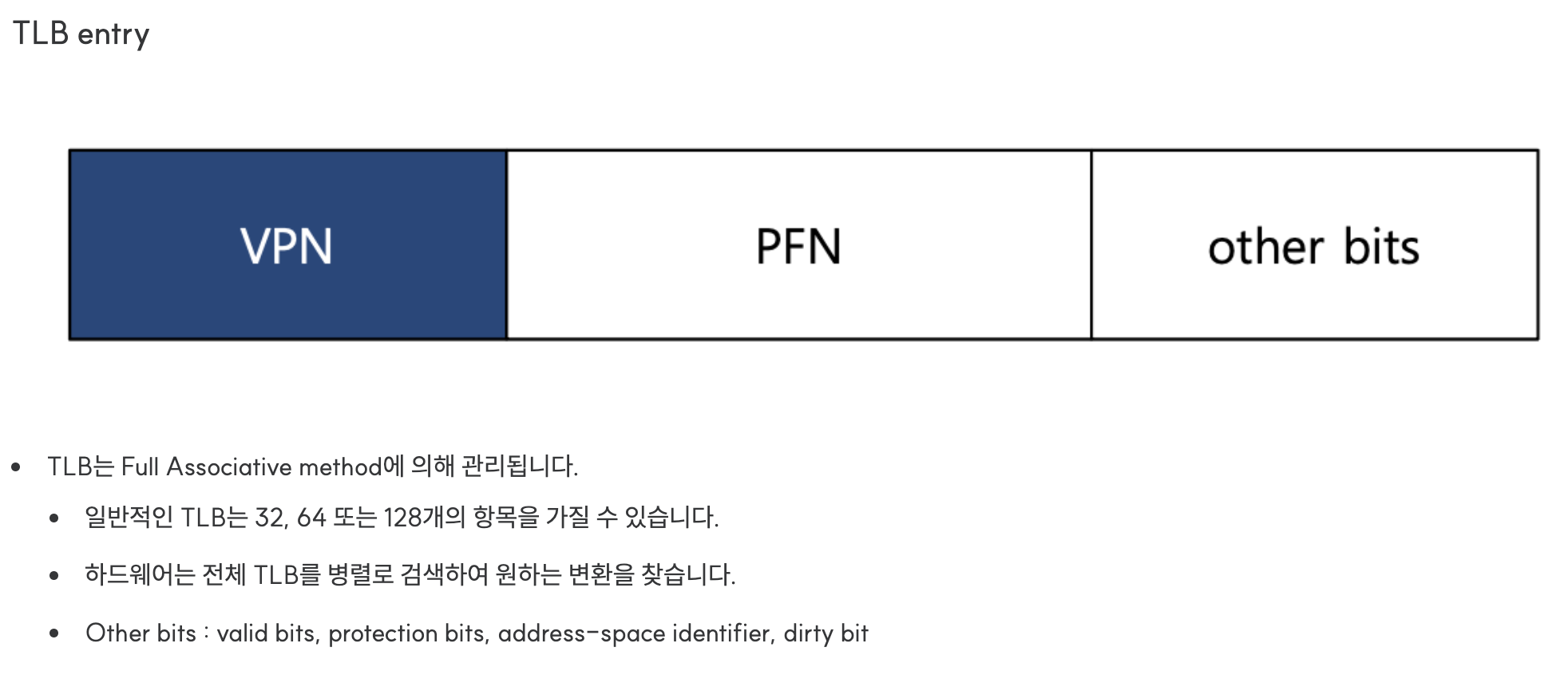

TLB의 구조

1. 항목 (Entry):

- TLB는 여러 개의 엔트리(entry)로 구성된다. 각 엔트리는 가상 페이지 번호(Virtual Page Number, VPN)와 물리 페이지 번호(Physical Page Number, PPN)를 포함한다.

2. 크기:

- TLB는 제한된 크기를 가지며, 일반적으로 수십에서 수백 개의 엔트리를 가질 수 있다. 크기가 너무 크면 접근 속도가 느려질 수 있다.

3. 연관도 : 가상 페이지 번호와 물리 페이지 번호의 매핑 방식을 의미

- 직접 매핑 (Direct Mapped TLB) : 한 개의 TLB 슬롯에 한 개의 페이지 엔트리만 저장.

각 가상 페이지 번호(VPN)는 특정 TLB 슬롯에 고정된 위치로 매핑.

한 개의 TLB 슬롯에는 오직 한 개의 페이지 엔트리만 저장.

- 완전 연관 매핑 : 모든 TLB 엔트리가 모든 페이지 엔트리에 대응 가능하여 충돌을 줄인다. 그러나 검색 시간이 길어질 수 있다.

- 집합 연관 매핑: TLB를 여러 개의 집합으로 나누고, 각 집합 내에서 완전 연관 매핑을 사용하여 성능과 복잡도의 균형을 맞춘다.

TLB의 작동 방식

1. TLB Lookup : 페이지 번호 병렬 검색 - 병렬 검색을 통해 TLB 전체 페이지 번호 병렬 조회

2. TLB Hit : TLB 내에 페이지 번호가 존재 - 페이지 번호와 연관되는 프레임 번호를 오프셋 번호(D)와 합쳐 물리주소 생성

(TLB의 히트율(캐시에 저장된 항목이 사용되는 비율)이 높을수록 시스템 성능이 더 좋아진다.)

3. TLB Miss : TLB내 페이지 번호 없음 - 페이지 테이블 참조해서 프레임 번호 검색, 프레임 번호와 오프셋 번호 합쳐 물리 주소 생성. 참조한 페이지의 페이지 번호 TLB 갱신

TLB 미스 처리:

- 소프트웨어 처리: 운영 체제가 TLB 미스를 처리. 유연하지만 느리다.

- 하드웨어 처리: 하드웨어가 직접 TLB 미스를 처리. 빠르지만 복잡하다.

4. Page Fault : TLB와 페이지 테이블 내 페이지 번호 없음 - 보조기억장치에서 페이지 반입 후 페이지테이블과 TBL 갱신

직접매핑 방식 vs TLB 비교

| 직접 매핑에 의한 주소변환 | TLB에 의한 주소변환 | |

| 사상방식 | Direct Mapping 물리 주소가 가상 주소로부터 직접 매핑 |

Association Mapping 연관 기억을 사용하여 가상 주소를 물리 주소로 매핑 |

| 페이지 테이블 위치 | 주기억장치 내부 | 고속의 특수 캐시 내부 (TLB) |

| 장단점 | 데이터 접근 시 주기억 장치 두 번 접근 | TLB 병렬 고속 탐색, 고비용, 적용 한계 |

페이지 교체

페이지 교체는 물리 메모리가 부족할 때, 사용되지 않는 페이지를 메모리에서 디스크로 이동시키고, 새로운 페이지를 메모리에 적재하는 과정이다. 이 과정은 메모리 관리에서 중요한 역할을 한다.

페이지 교체와 TLB

페이지 교체 시 TLB에 존재하는 항목도 업데이트해야 한다. LRU(Least Recently Used) 알고리즘이 자주 사용되며, 가장 오랫동안 사용되지 않은 페이지를 교체하는 방식이다. TLB도 이와 유사한 방식으로 자주 사용되지 않은 항목을 교체하여 최신 데이터를 유지한다.

성능 최적화 기법

1. TLB 사전 로드 (Prefetching):

- 예상되는 메모리 접근 패턴을 기반으로 미리 TLB를 채워 TLB 미스를 줄인다.

2. 다중 레벨 TLB (Multi-level TLB):

- L1 TLB, L2 TLB와 같이 다중 레벨로 TLB를 구성하여 TLB 히트율을 높인다. L1 TLB는 작고 빠르며, L2 TLB는 상대적으로 크고 느리다.

3. 페이지 크기:

- 큰 페이지를 사용하면, 동일한 TLB 엔트리에 더 많은 메모리를 매핑할 수 있어 TLB 히트율을 높일 수 있다. 그러나 큰 페이지는 메모리 낭비를 초래할 수 있다.

4. TLB Shootdown:

- 멀티코어 시스템에서 페이지 테이블이 변경될 때, 모든 코어의 TLB를 업데이트하는 작업이다. 이를 효율적으로 처리하여 TLB 일관성을 유지한다.

TLB와 관련된 이슈

1. 컨텍스트 스위칭:

- 프로세스 간의 전환이 빈번할 경우, TLB의 내용이 무효화되어 TLB 미스가 증가할 수 있다. 이를 줄이기 위해, 컨텍스트별 TLB 항목을 유지하는 기법(예: Address Space Identifier, ASID)을 사용한다.

-> TLB 플러시와 프로세스 식별자(Tagging)으로 해결한다.

(tagging : 각 TLB 엔트리에 프로세스 ID(또는 주소공간 ID)를 추가

2. TLB 플러시:

- 가상 메모리 공간이 변경되면, TLB의 관련 항목을 무효화해야 한다. 플러시 작업은 비용이 크기 때문에 효율적으로 관리해야 한다.

3. 보안 문제:

- TLB와 관련된 보안 취약점(예: TLBleed)도 연구되고 있다. 이러한 취약점을 방지하기 위해 TLB 디자인에서 보안성을 고려해야 한다.

TLB가 성능을 향상시키는 방법: 히트율과 지역성

TLB는 시스템 성능을 크게 향상시킬 수 있다. 이는 두 가지 주요 개념인 히트율과 지역성을 통해 이루어진다.

히트율:

TLB 히트율은 TLB에서 필요한 가상 주소를 찾을 확률을 의미한다. 높은 히트율은 TLB가 효과적으로 작동하고 있음을 나타내며, 이는 주소 변환 시간을 크게 줄여 시스템 성능을 향상시킨다. 히트율을 높이기 위해, TLB는 자주 사용되는 페이지 테이블 항목을 저장하고 관리한다.

지역성:

메모리 접근 패턴에는 시간 지역성(temporal locality)과 공간 지역성(spatial locality)이 있다. 시간 지역성은 최근에 접근한 메모리 위치가 다시 접근될 가능성이 높다는 것을 의미하며, 공간 지역성은 접근한 메모리 위치 근처의 메모리가 곧 접근될 가능성이 높다는 것을 의미한다. TLB는 이러한 지역성 원리를 활용하여 자주 접근하는 페이지 테이블 항목을 캐시에 저장하고, 이를 통해 TLB 히트율을 높인다.

결론

TLB는 CPU의 성능에 중요한 역할을 하며, 다양한 최적화 기법을 통해 TLB의 히트율을 높이는 것이 중요하다. TLB의 구조와 동작 방식을 이해하면, 가상 메모리 시스템의 효율성을 높이는 데 기여할 수 있다.

TLB는 페이지 테이블의 작은 부분을 고속 캐시에 저장하여 페이지 테이블 전체를 참조하지 않고도 빠른 주소 변환을 가능하게 한다. 페이지 테이블이 크고 복잡할수록, TLB는 이를 최적화하여 시스템 성능을 향상시키는 역할을 한다. TLB는 자주 사용되는 페이지 테이블 항목을 저장함으로써 메모리 접근 시간을 줄여준다.

Summary

=> TLB는 CPU 내에서 가상 주소를 물리 주소로 빠르게 변환하는 고속 캐시 메모리이다.

=> TLB는 MMU에 통합되어 주소 변환 속도를 높이고, 시스템 성능을 최적화한다.

장점:

1. 주소 변환 속도 향상

2. 메모리 액세스 최적화

3. 시스템 성능 향상

단점:

1. 제한된 크기로 인해 TLB 미스 발생 가능

2. 컨텍스트 스위칭 시 TLB 플러시 필요

3. 보안 취약점 존재 가능

비유로 설명하는 TLB

TLB를 도서관과 책장으로 비유할 수 있다. 도서관에서 특정 책을 찾는다고 생각해보자.

- 도서관: 페이지 테이블

- 도서관은 모든 책이 정리되어 있는 거대한 장소다. 이곳에서 책을 찾으려면 많은 시간이 걸린다.

- 도서관의 단골 독자: TLB

- 도서관에 자주 오는 단골 독자는 자신이 자주 찾는 책들이 어디에 있는지 정확히 알고 있다. 그래서 단골 독자는 도서관 전체를 뒤지지 않고도 필요한 책을 빨리 찾을 수 있다.

- 도서관 사서: MMU

- 사서는 도서관에서 책을 찾고 빌려주는 사람이다. 사서가 책을 찾을 때, 단골 독자의 도움을 받으면 빠르게 책을 찾을 수 있다. 그렇지 않으면 직접 서가를 뒤져야 한다.

'CS' 카테고리의 다른 글

| CS_동기화(Synchronization)_스핀락, 뮤텍스, 세마포어 (0) | 2024.06.30 |

|---|---|

| CS_운영체제_Paging: Smaller Table (0) | 2024.06.25 |

| CS_운영체제_세그먼테이션, 페이징 (1) | 2024.06.23 |

| CS_운영체제_가상메모리 요구 페이징과 페이지 폴트 (1) | 2024.06.23 |

| CS_운영체제_PCB & Context Switching (0) | 2024.06.18 |